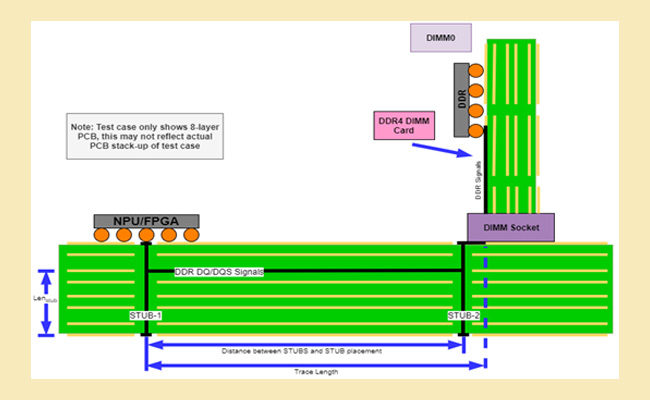

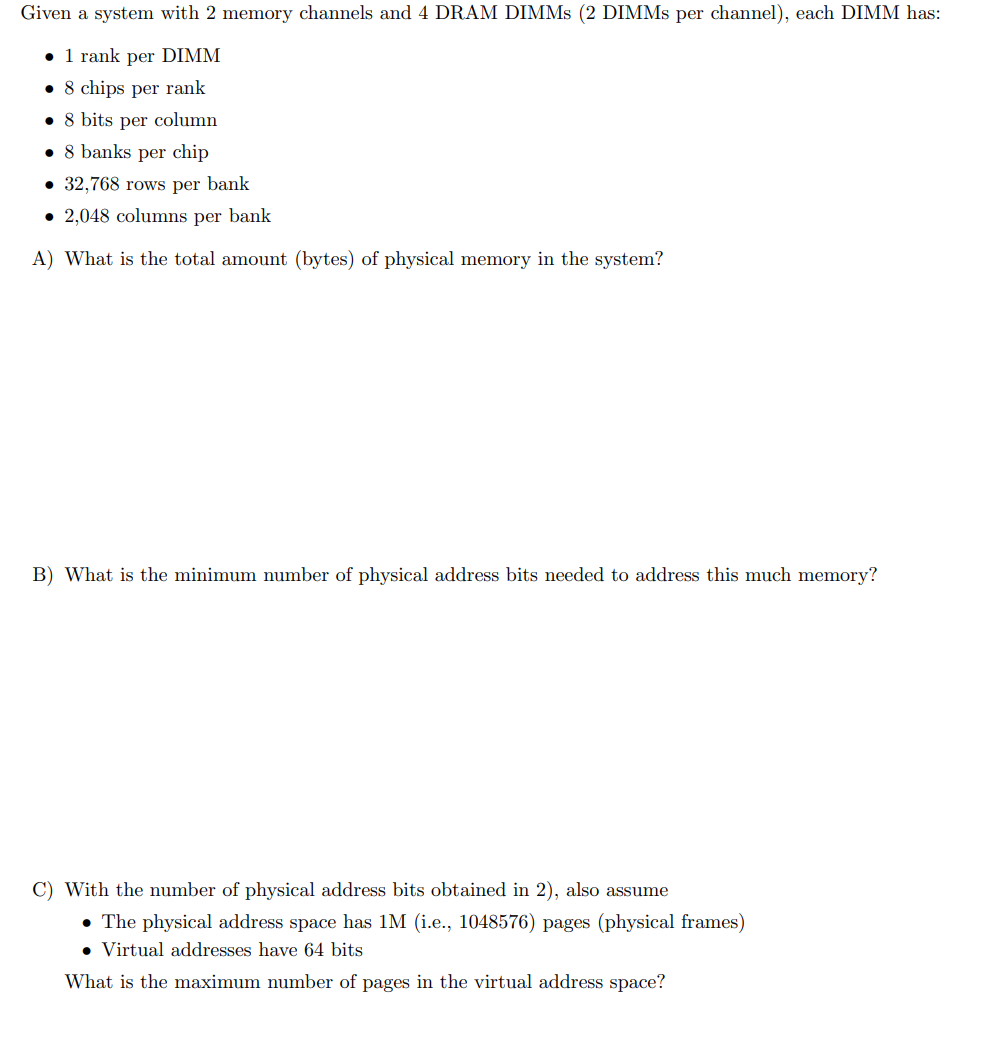

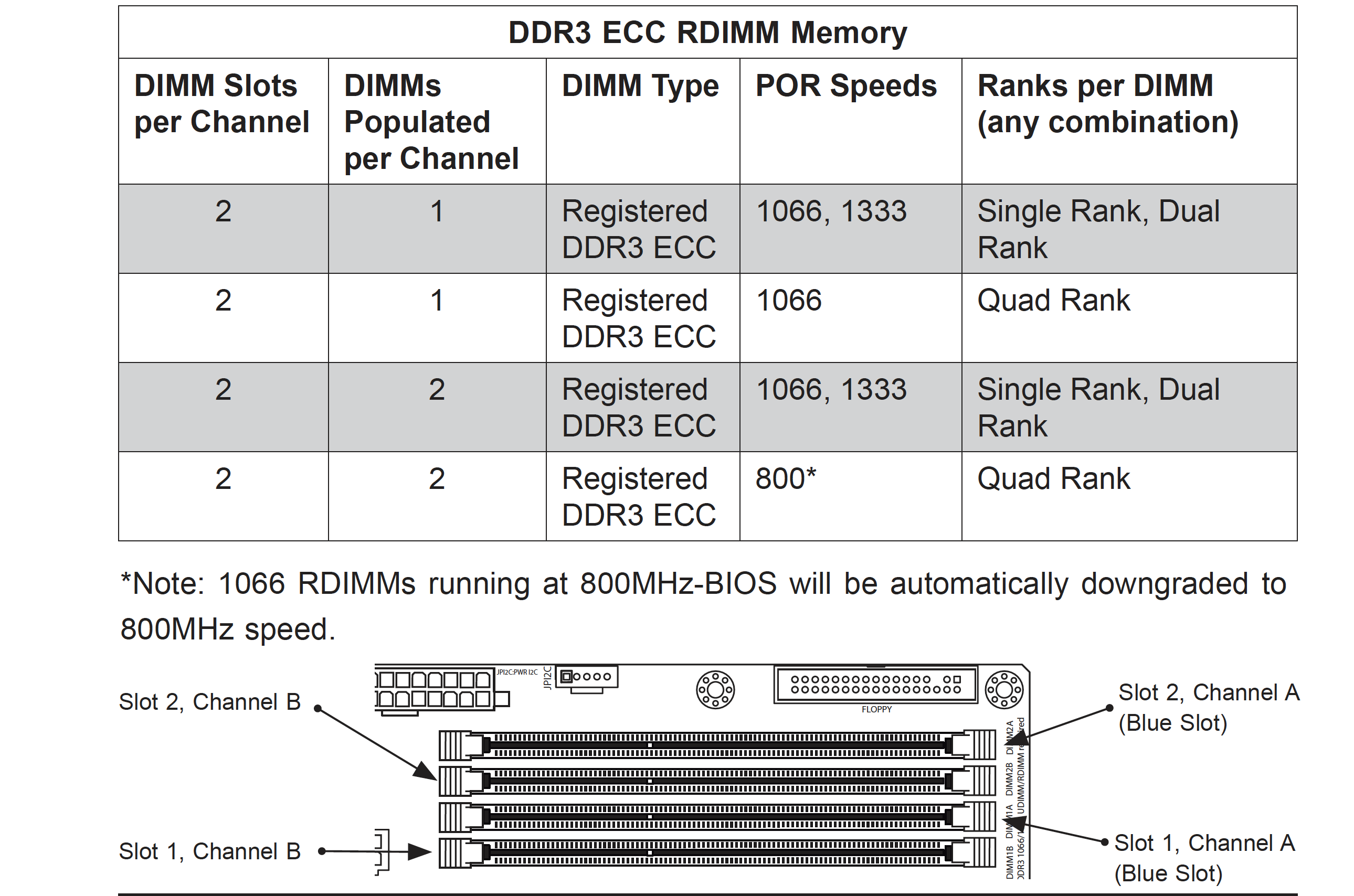

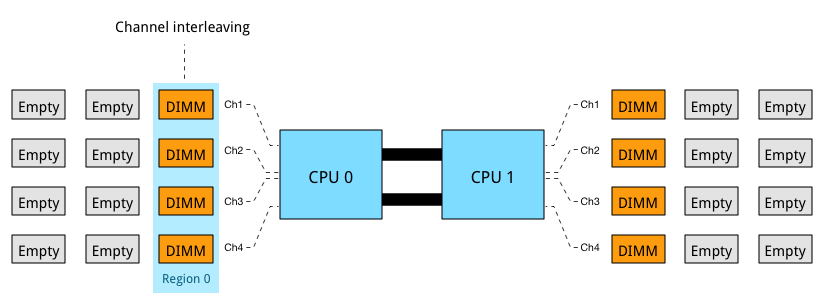

Memory channel-Memory controller is connected to DRAM modules (DIMMs)... | Download Scientific Diagram

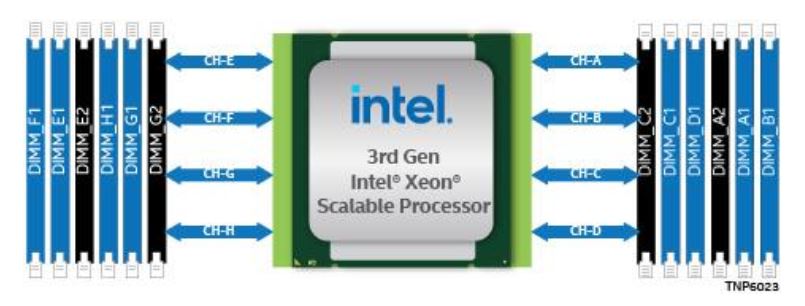

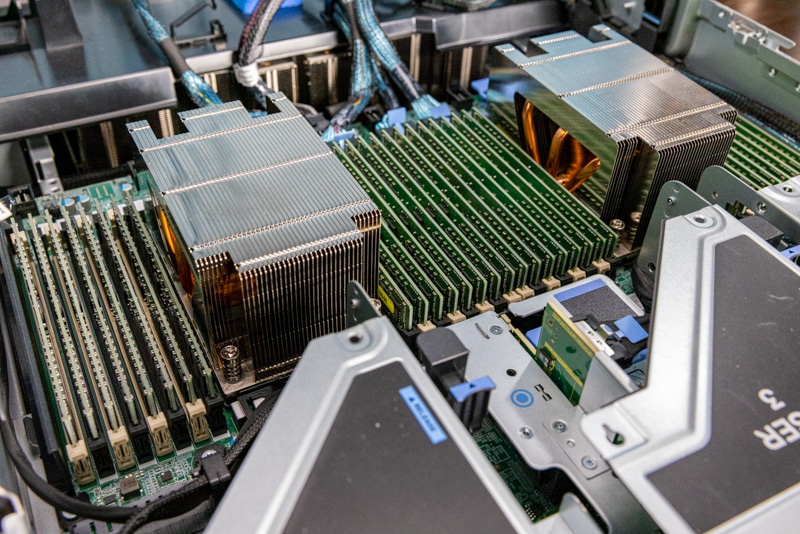

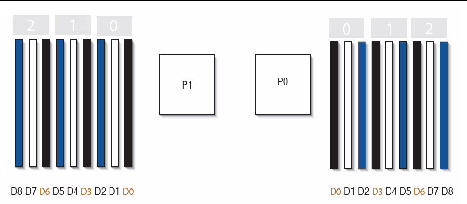

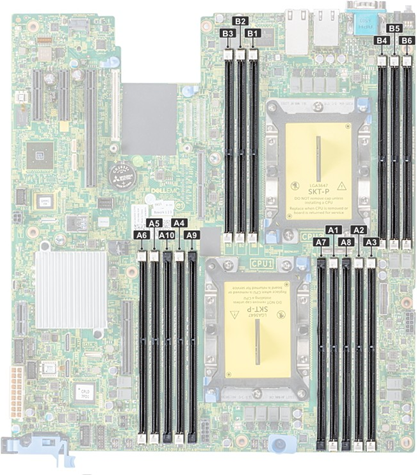

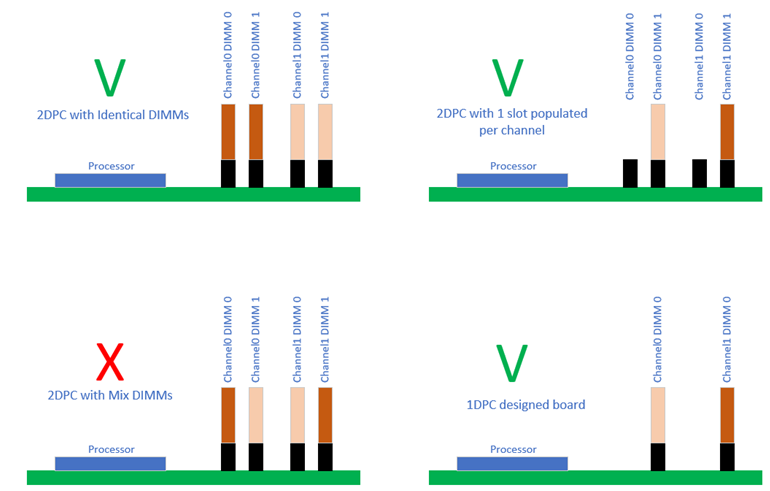

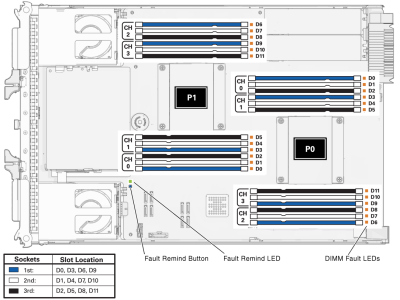

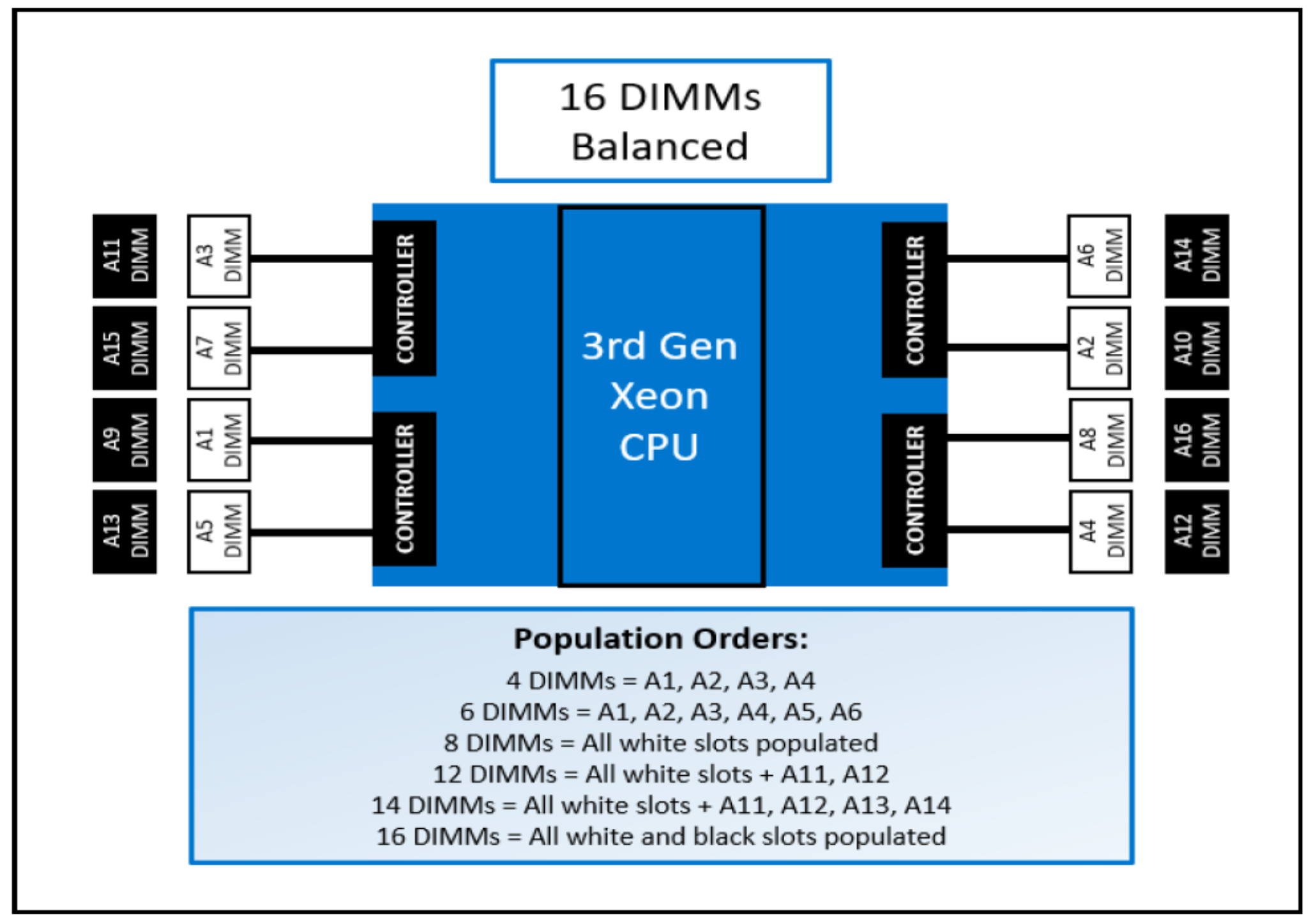

Memory channel population | Memory Population Rules for 3rd Generation Intel Xeon Scalable Processors on PowerEdge Servers | Dell Technologies Info Hub

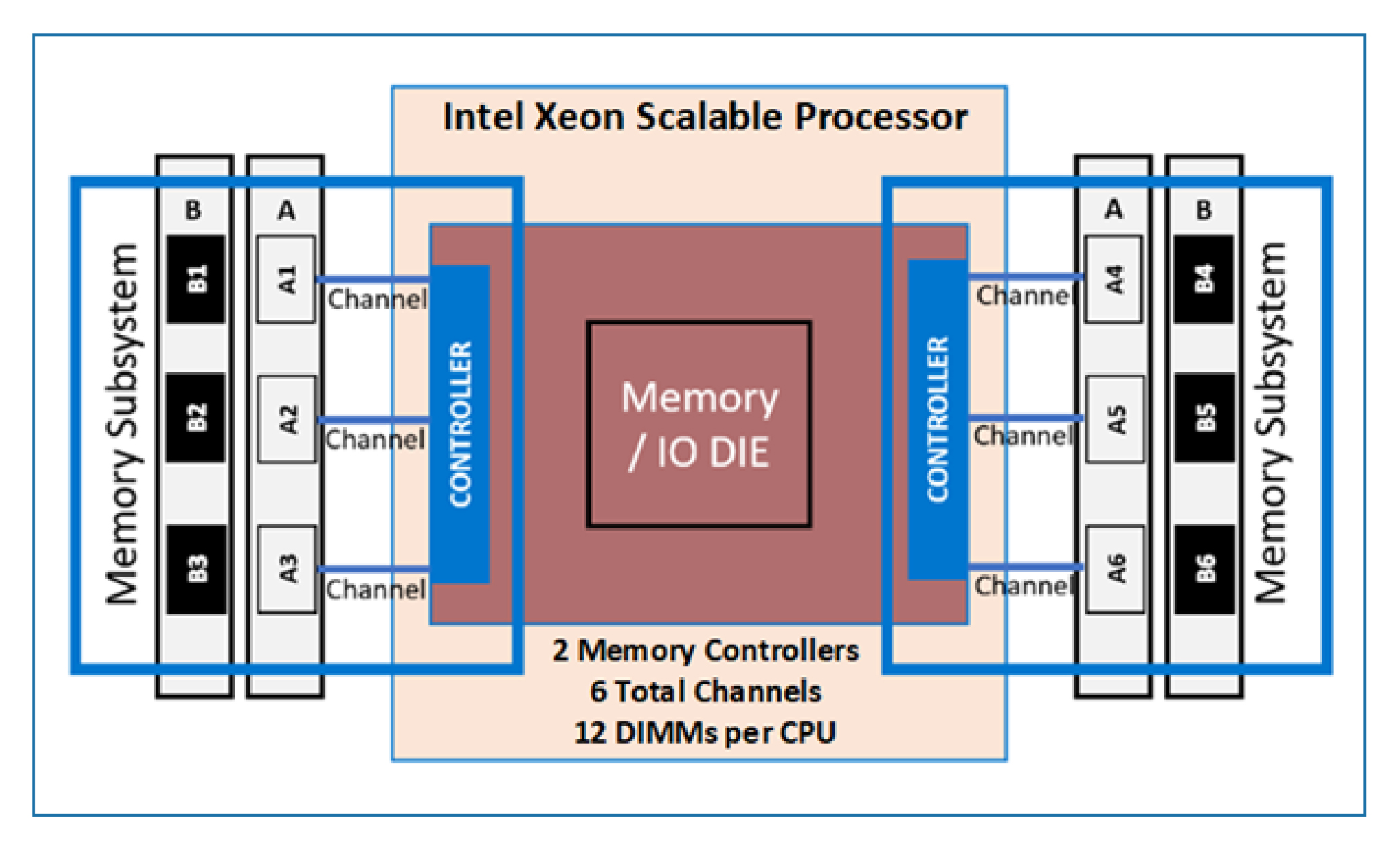

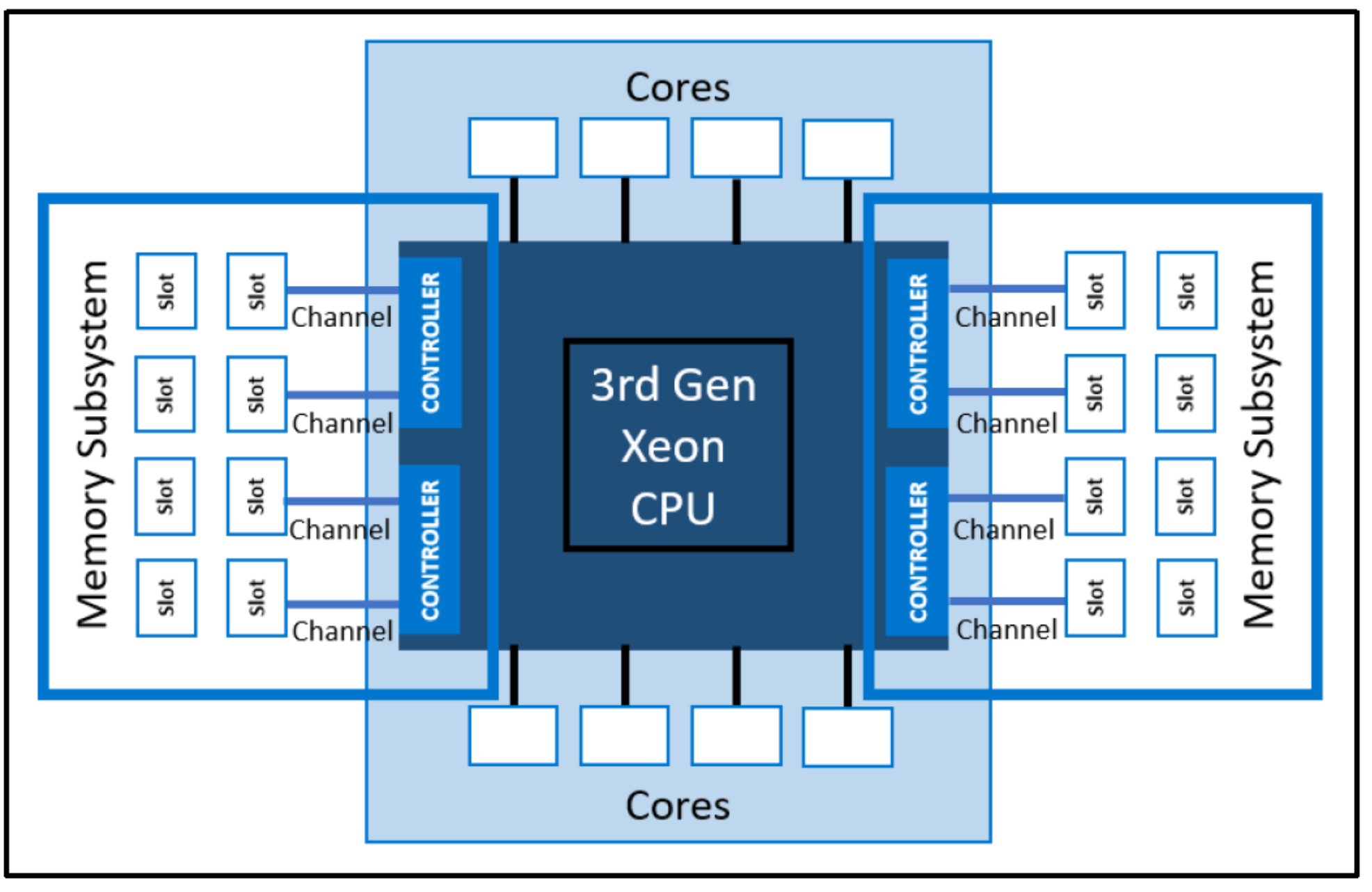

Memory topography and terminology | Memory Population Rules for 3rd Generation Intel Xeon Scalable Processors on PowerEdge Servers | Dell Technologies Info Hub

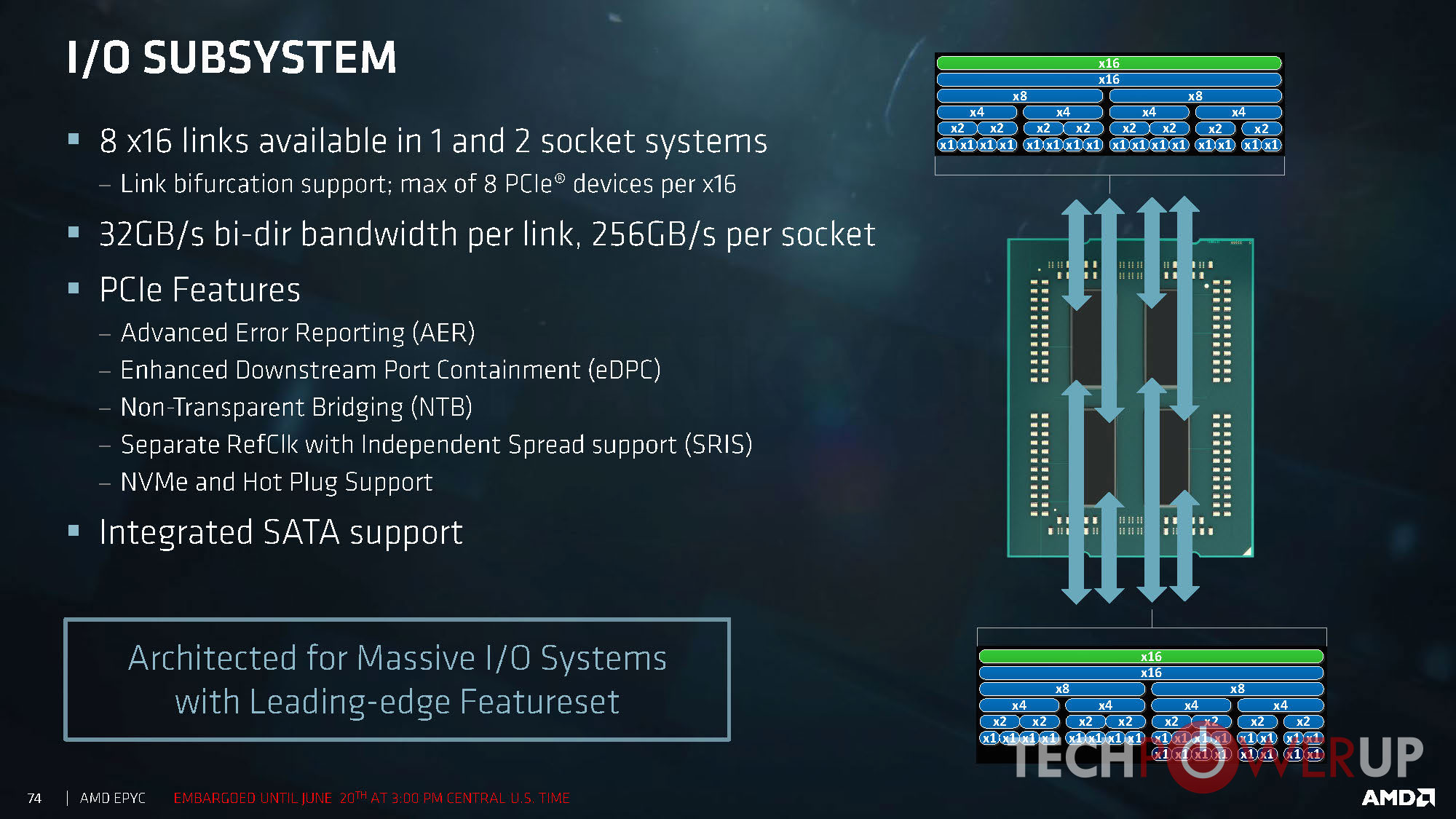

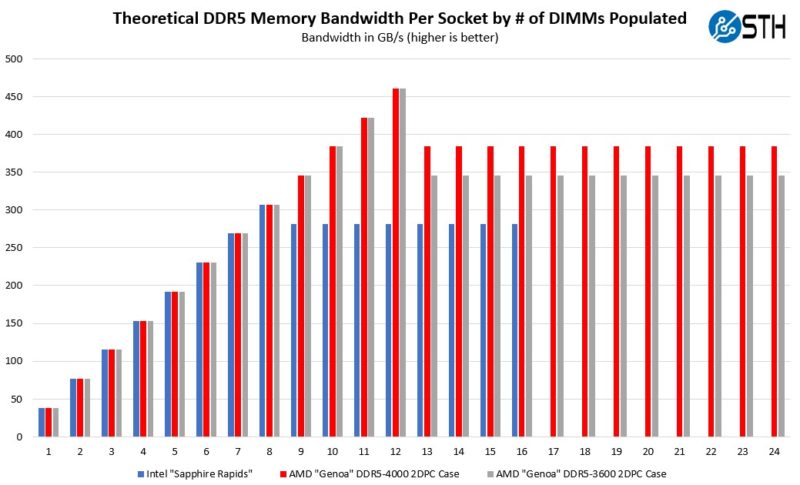

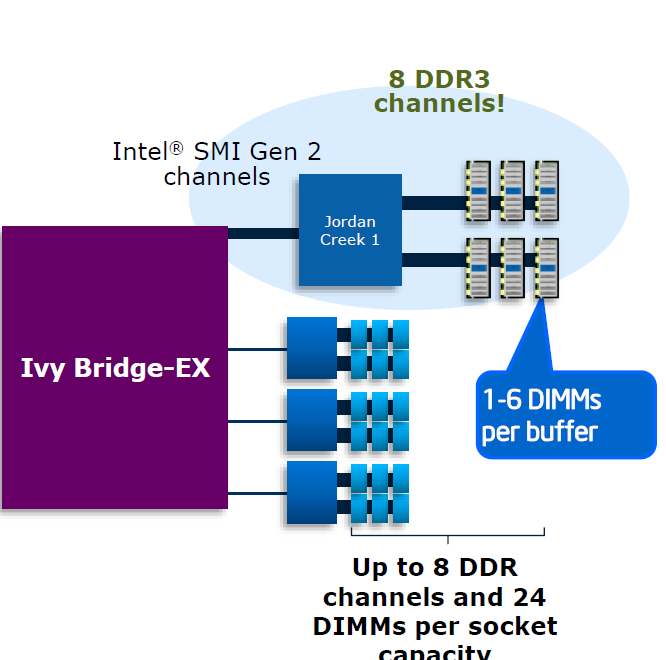

Now with High Bandwidth Memory - The Intel Xeon E7 v2 Review: Quad Socket, Up to 60 Cores/120 Threads

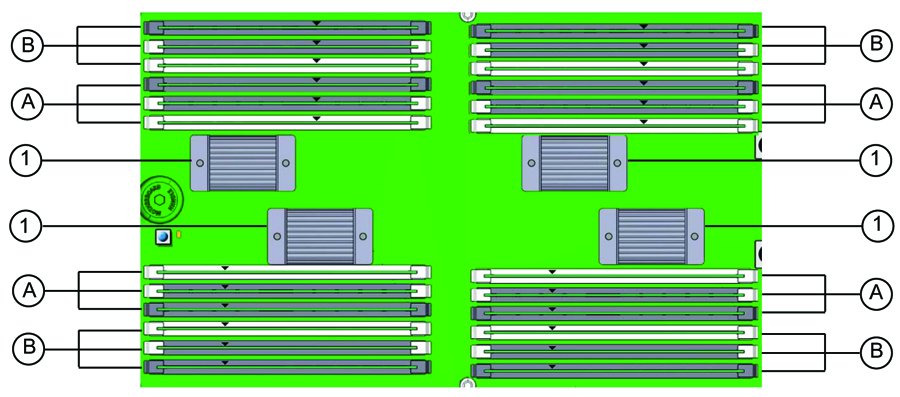

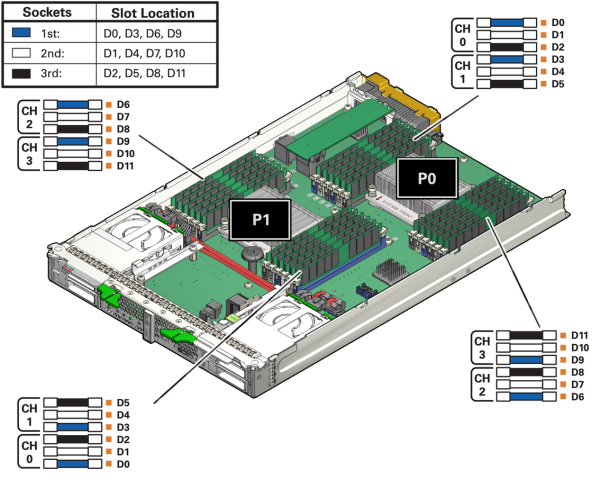

Population rules for DIMMs in HPE Gen10 servers with Intel Xeon Scalable processors technical white paper